5G Baseband Algorithm Testbed

Demos Links

- Link 1

- Link 2

Objective of the Project

This project offers a fully-equipped setup for implementing and evaluating the 5G baseband algorithms. These algorithms constitute a sophisticated suite of mathematical and computational procedures that oversee the encoding, transmission, and reception of data in the 5G physical layer.The design of efficient algorithm is central to realize the promise of 5G technology of achieving lightning-fast data rates, small latency, and a robust and uninterrupted connectivity experience.

In essence, this project is providing the essential infrastructure for the development and evaluation of these pivotal baseband algorithms.

Scope

In the 5G baseband algorithm testbed project, we’ve collaborated with IIT Madras and CeWit to design and test the baseband algorithms tailored for 5G NR. This project encompass three crucial components:

1. Channel Estimation and Channel Equalization Algorithms (in collaboration with IIT Madras): Channel estimation involves the acquisition of channel gain estimates from received demodulation reference symbols (DMRS) at user terminals. The acquired channel estimates are subsequently utilized by the channel equalizer to detect the transmitted information symbols from received data symbols.

2. Blind Decoding Algorithm for PDCCH (in collaboration with CeWit): Proper decoding of downlink control information transmitted on the Physical Downlink Control Channel (PDCCH)is paramount. Traditional PDCCH decoding methods, given their complexity, sometimes fail to complete execution within the allotted time frame. This can necessitate retransmission, resulting in increased communication overhead. In this project, we’ve implemented a PDCCH decoder based on DMRS correlation. Notably, this decoder exhibits significantly reduced execution time and complexity when compared with conventional PDCCH decoding methods.

3. A setup for design and testing of baseband algorithms: Our project encompasses the establishment of a comprehensive suite of tools for designing baseband algorithms for 5G NR. Here’s a brief overview of the workflow:

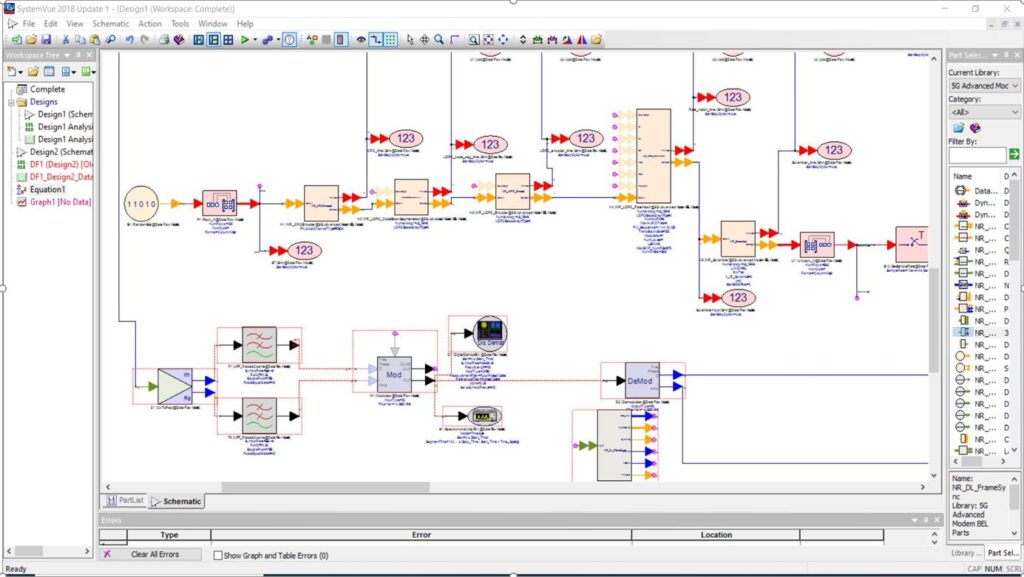

- Design and Simulation: We employ SystemVue as our primary tool for designing and rigor-ously testing 5G NR physical layer algorithms in a simulated environment as shown in Figure 1.

- Real-time Testing: The source code generated by SystemVue undergoes real-time testing using a 5G NR vector signal analyzer/generator as shown in Figure 2.

Figure 1: Design Using SystemVue

Figure 2: Real-time testing with vector signal analyzer/generator

- Standalone Testing on FPGA: We compile the verified source code using the Vivado HLX suite. This compiled code is then executed on a Zync UltrascaleZCU102 FPGA in real-time for testing as shown in Figure 3.

This design and verification setup we’ve established holds immense value for both industry and academia. It serves as a robust platform for the development of baseband algorithms tailored for 5G NR-based applications. Whether you’re in the field of research or industry, our setup equips you with the tools needed to drive innovation in the exciting realm of 5G NR technology.

Figure 3: Real time execution on Zync Ultrascale ZCU102 FPGA

Value Proposition

• Comprehensive infrastructure for the development and evaluation of baseband algorithms de-signed for 5G NR.

• Tools and Resources:

– Utilization of SystemVue for the creation of C and HDL code for 5G NR L1 modules.

– Employing the Vivado HLx suite and Zync Ultrascale ZCU102 FPGA for real-time code execution and in-depth performance analysis.

– Utilizing vector signal analyzers, generators, and vector transceivers to evaluate both

the reliability and performance of 5G NR signals that have been generated using the

SystemVue platform.